電池iv曲線右上角不直的原因及解決方法

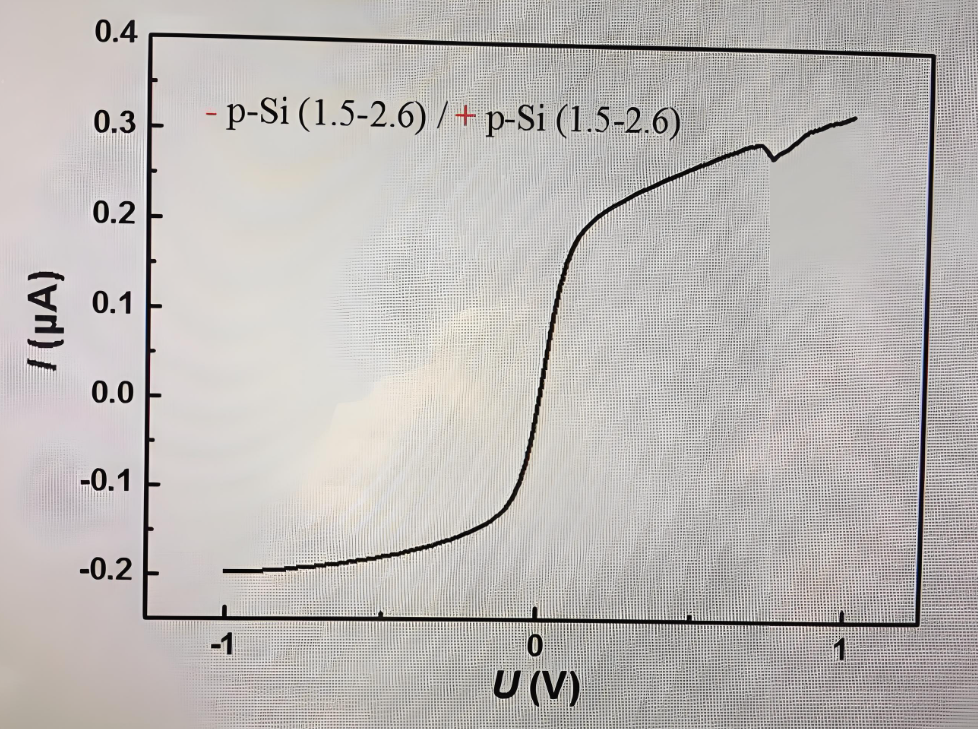

電池I-V曲線(電流-電壓曲線)右上角不直,通常表現為(wei) 曲線在高電壓區域(接近開路電壓Voc)出現彎曲、上翹或波動,這主要與(yu) 電池內(nei) 部的非理想電學特性有關(guan) 。以下是具體(ti) 原因及解決(jue) 方法:

一、原因分析

串聯電阻(Rs)過高

1)表現:曲線在高電壓區域斜率增大,呈現“上翹”趨勢。

2)機製:串聯電阻包括電極材料電阻、接觸電阻、體(ti) 材料電阻等。當Rs過大時,高電壓下電流通過電阻產(chan) 生的壓降(I×Rs)顯著,導致實際輸出電壓降低,曲線偏離理想直線。

3)常見場景:

電極與(yu) 半導體(ti) 材料接觸不良(如燒結溫度不足、導電膠厚度不均)。

金屬電極線寬過窄或厚度不足,導致電流傳(chuan) 輸路徑狹窄。

電池體(ti) 材料(如矽片)存在高摻雜區域或晶界缺陷,增加電阻。

並聯電阻(Rsh)過低

1)表現:曲線在高電壓區域出現“下垂”或波動,甚至接近開路電壓時電流不為(wei) 零。

2)機製:並聯電阻反映電池漏電流路徑(如邊緣漏電、表麵複合、PN結缺陷)。當Rsh過低時,漏電流在高電壓下顯著增加,導致輸出電流偏離理想值。

3)常見場景:

電池邊緣未完全絕緣,存在邊緣漏電。

表麵鈍化層(如SiNx、Al2O3)質量差,導致表麵複合嚴(yan) 重。

PN結存在局部缺陷(如位錯、雜質聚集),形成漏電通道。

空間電荷區複合(SCR複合)

1)表現:曲線在高電壓區域斜率變化,可能伴隨輕微彎曲。

2)機製:在PN結空間電荷區,載流子可能通過複合中心(如缺陷、雜質)發生複合,導致電流損失。高電壓下,空間電荷區寬度增加,複合效應增強,影響曲線線性度。

3)常見場景:

矽片晶格缺陷密度高(如多晶矽晶界)。

擴散工藝控製不當,導致PN結摻雜剖麵不理想。

測試係統誤差

1)表現:曲線重複性差,或與(yu) 其他設備測試結果不一致。

2)機製:測試夾具接觸不良、電子負載精度不足、光強不均勻等可能導致數據失真。

3)常見場景:

夾具與(yu) 電池電極接觸壓力不足,導致接觸電阻波動。

太陽光模擬器光強均勻性差(>±2%),局部光照過強或過弱。

電子負載采樣速率不足,無法捕捉快速電流變化。

二、解決方法

降低串聯電阻(Rs)

1)優(you) 化電極設計:

增加電極線寬或厚度,減少電流傳(chuan) 輸路徑電阻。

使用高導電性材料(如銀漿、銅漿)替代低導電性材料。

優(you) 化燒結溫度和時間,確保電極與(yu) 半導體(ti) 材料形成良好歐姆接觸。

控製導電膠或焊料的塗覆厚度,避免局部過厚導致接觸不良。

選擇低電阻率矽片(如N型單晶矽)。

優(you) 化摻雜工藝,減少高摻雜區域電阻。

提高並聯電阻(Rsh)

1)加強邊緣絕緣:

在電池邊緣塗覆絕緣膠(如環氧樹脂)或激光刻槽隔離,防止邊緣漏電。

使用高質量鈍化層(如PECVD沉積的SiNx)減少表麵複合。

引入氫化處理或場效應鈍化技術,修複表麵缺陷。

通過吸雜工藝(如磷擴散吸雜)減少矽片中的金屬雜質。

優(you) 化擴散工藝,避免PN結摻雜剖麵出現“尖峰”或“尾巴”。

抑製空間電荷區複合

1)選擇低缺陷材料:

使用單晶矽或高質量多晶矽,減少晶界缺陷。

控製擴散溫度和時間,形成理想的摻雜剖麵(如漸變結)。

在電池背麵沉積高摻雜層(如鋁背場),減少背麵複合。

排除測試係統誤差

1)檢查測試設備:

使用四線法測量接觸電阻,排除夾具接觸電阻影響。

定期校準太陽光模擬器,確保光強均勻性(≤±2%)和穩定性(≤±0.5%/分鍾)。

選擇高精度電子負載(如 Keithley 2400 係列),確保采樣速率和分辨率滿足要求。

控製測試溫度在25℃±1℃,避免溫度波動影響結果。

減少環境光幹擾,使用遮光罩或暗室進行測試。

2)改善接觸工藝:

3)減少體(ti) 材料電阻:

2)優(you) 化表麵鈍化:

3)修複PN結缺陷:

2)優(you) 化擴散工藝:

3)引入背表麵場(BSF):

2)優(you) 化測試環境:

三、案例驗證

案例1:某晶矽電池I-V曲線右上角上翹,經檢測發現電極燒結溫度不足導致接觸電阻過高。通過提高燒結溫度至850℃,Rs從(cong) 1.2Ω降低至0.8Ω,曲線恢複直線。

案例2:某PERC電池I-V曲線右上角下垂,檢查發現邊緣未塗覆絕緣膠導致漏電。補充絕緣膠後,Rsh從(cong) 500Ω提升至2000Ω,曲線線性度顯著改善。

愛疆微信

愛疆微信

在線

在線 谘詢

谘詢

關注

關注